Hi everyone:

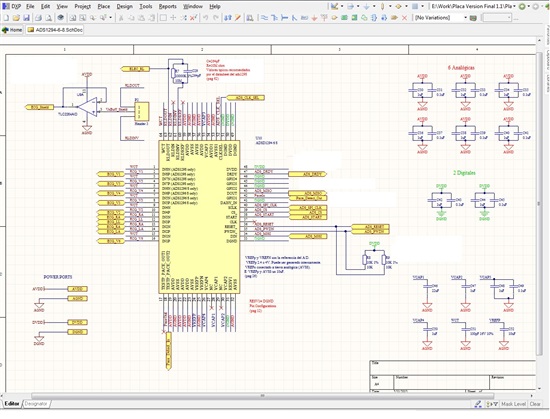

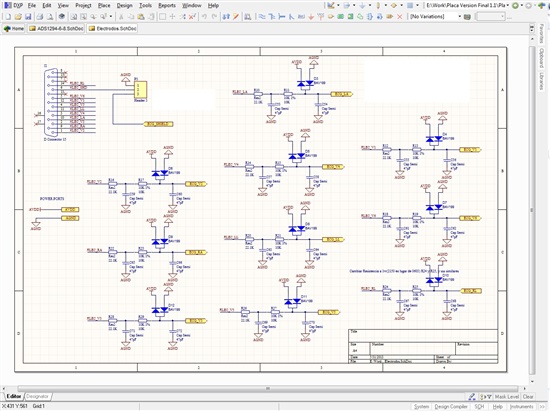

Here is my problem. Lead off detection, pacemaker detection and all function related with ECG are working great but I can't get a value of CMRR higher than 74dB. I'm entering a signal of 16Vpp and 60Hz. I think the problem is related with right leg drive.The RLD Ad1298 internal buffer could be used with (AVDD+AVSS)/2 or External reference or WCT. I had tested all variants and I can improve the results. Also I had used Appnote "SBAA188-july 2011 Improving Common-Mode Rejection Using the Right-Leg Drive Amplifier" and nothing new is cought. Yesterday I have used and external circuit using TL2264AI and the configuration at page 63 of ADS1298 datasheet. I haven't any ideas.

I'm using MSP430F5529 to communicate with the ADS1298. This is my register configuration.

#define CONFIG1 0x86// 0x06 //Lower power mode //1000 0110 0x86 high resolution

#define CONFIG2 0x10

#define CONFIG3 0xDC//0xDE//0xDC//

#define LOFF 0x03//0x03//0xF3//0xE3//

#define CH1SET 0x00

#define CH2SET 0x00

#define CH3SET 0x00

#define CH4SET 0x00

#define CH5SET 0x00

#define CH6SET 0x00

#define CH7SET 0x00

#define CH8SET 0x00

#define RLD_SENSP 0x03 // 0x06//

#define RLD_SENSN 0x01 // 0x02

#define LOFF_SENSP 0XFF // 0x00

#define LOFF_SENSN 0x00 // 0xFF //0x02 // 0x00

#define LOFF_FLIP 0x00

#define LOFF_STATP 00h //read only

#define LOFF_STATN 0x00 //read only

#define GPIO 0x0F

#define PACE 0x03

#define RESP 0x00

#define CONFIG4 0x06

#define WCT1 0x0a

#define WCT2 0xE3

I have spent an entire month triying to solve this, but I couldn't. So If someone can help, I would really appreciate it .

Regards

Miguel